## EXPANDED CONTROLLER INTERFACE DEVICE INPUT/OUTPUT CAPABILITIES AND CID SOFTWARE COORDINATION

Final Report KLK235 N07-04

National Institute for Advanced Transportation Technology University of Idaho

Ahmed Abdel-Rahim; Brian Johnson Zhen Li; Eugene Bordenkircher; Joel Alberts; Sanjeev Giri; Mark Hutchinson

March 2007

### DISCLAIMER

The contents of this report reflect the views of the authors, who are responsible for the facts and the accuracy of the information presented herein. This document is disseminated under the sponsorship of the Department of Transportation, University Transportation Centers Program, in the interest of information exchange. The U.S. Government assumes no liability for the contents or use thereof.

| 1. Report No.                                                                          | 2. Govern          | ment Accession No.      | 3.                       | Recipient's C    | atalog No.            |  |  |  |

|----------------------------------------------------------------------------------------|--------------------|-------------------------|--------------------------|------------------|-----------------------|--|--|--|

| 4. Title and Subtitle                                                                  | 5.                 | Report Date             |                          |                  |                       |  |  |  |

| Expanded Controller Interface Device Inp                                               | are Dec            | cember 2006             |                          |                  |                       |  |  |  |

| Coordination                                                                           | 6.                 | Dorforming ()           | reganization Code        |                  |                       |  |  |  |

|                                                                                        | 0.                 | -                       | rganization Code         |                  |                       |  |  |  |

|                                                                                        |                    | KLK235                  |                          |                  |                       |  |  |  |

| 5.Author(s)                                                                            | 8.                 | -                       | rganization Report No.   |                  |                       |  |  |  |

| Ahmed Abdel-Rahim; Brian Johnson with                                                  | -                  | ene Bordenkircher, Joel |                          | N07-04           |                       |  |  |  |

| Alberts, Sanjeev Giri and Mark Hutc                                                    | hinson             |                         |                          |                  |                       |  |  |  |

| 9. Performing Organization Name and                                                    | Address            |                         | 10.                      | Work Unit No     | D. (TRAIS)            |  |  |  |

| National Institute for Advanced Tran                                                   | sportation Tec     | hnology                 |                          |                  |                       |  |  |  |

| University of Idaho                                                                    |                    |                         |                          |                  |                       |  |  |  |

| PO Box 440901; 115 Engineering Pl                                                      | nysics Building    | 5                       | 11.                      | Contract or G    | rant No.              |  |  |  |

| Moscow, ID 838440901                                                                   |                    |                         |                          | DTRS98-G-00      | )27                   |  |  |  |

| 12. Sponsoring Agency Name and Addr                                                    | ess                |                         | 13.                      | Type of Repo     | rt and Period Covered |  |  |  |

| US Department of Transportation                                                        |                    |                         |                          | Final Report:    | August 2004-December  |  |  |  |

| Research and Special Programs Adn                                                      | inistration        |                         |                          | 2005             |                       |  |  |  |

| 400 7 <sup>th</sup> Street SW                                                          |                    |                         |                          |                  |                       |  |  |  |

| Washington, DC 20509-0001                                                              |                    |                         |                          |                  |                       |  |  |  |

|                                                                                        |                    |                         | 14.                      | Sponsoring A     | gency Code            |  |  |  |

|                                                                                        |                    |                         |                          | USDOT/RSPA/DIR-1 |                       |  |  |  |

| Supplementary Notes:                                                                   |                    |                         |                          |                  |                       |  |  |  |

| Supprenientary Potes.                                                                  |                    |                         |                          |                  |                       |  |  |  |

| 16. Abstract                                                                           |                    |                         |                          |                  |                       |  |  |  |

| The controller interface device (CID) is the                                           |                    |                         |                          |                  |                       |  |  |  |

| had two objectives: the first was to expan<br>connections limit performance. The secor |                    |                         |                          |                  |                       |  |  |  |

| and testing a prototype to use the CID and                                             |                    |                         |                          |                  |                       |  |  |  |

| standards.                                                                             | C" ( 1 '1          |                         |                          | 1 / 1' 1         |                       |  |  |  |

| This final report is made in two parts. The capability for the CID. The second part di |                    |                         |                          |                  |                       |  |  |  |

| introduced in and is presented in the form                                             | of a paper title   | ed: "Real-Time Playback | Hardwa                   | re-in-the-Loop S | Simulation of Traffic |  |  |  |

| Systems," presented at IECON 2005, 32n                                                 |                    |                         |                          |                  |                       |  |  |  |

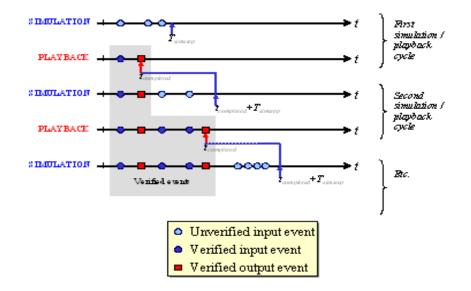

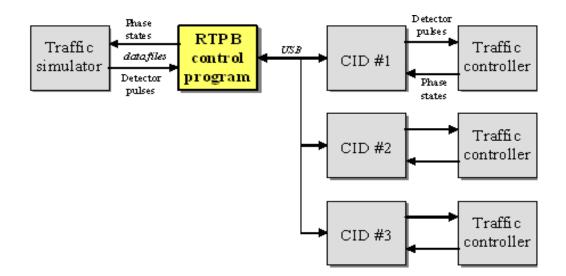

| the development of a software-controlled<br>loop simulation of traffic systems. The to |                    |                         |                          |                  |                       |  |  |  |

| loop simulation of traine systems. The to                                              |                    |                         |                          |                  |                       |  |  |  |

| used in power systems as a cheap alternat                                              | es RTPB            | is the only pos         | sible simulation method. |                  |                       |  |  |  |

| This paper presents the application of RT                                              | affic cont<br>ment | troller hardware        | <u>.</u>                 |                  |                       |  |  |  |

| 17. Key Words<br>Hardware-in-the-loop simulation; traffic s                            | able to the publi  | ic through the National |                          |                  |                       |  |  |  |

| controllers; traffic simulation; real-time c                                           |                    | Springfield, VT         | -                        |                  |                       |  |  |  |

|                                                                                        |                    |                         |                          |                  |                       |  |  |  |

|                                                                                        | 21. INO.           | of Pages                | 22. Price                |                  |                       |  |  |  |

| Unclassified                                                                           | Unclassifie        | ju                      |                          |                  |                       |  |  |  |

Form DOT F 1700.7 (8-72)

Reproduction of completed page authorized

### TABLE OF CONTENTS

| EXECUTIVE SUMMARY 1                                               |

|-------------------------------------------------------------------|

| PART 1: SYNCHRONOUS DATA LINK CONTROL INTERFACE FOR INTERFACE FOR |

| CONTROLLER INTERFACE DEVICE TO TRAFFIC CONTROLLER COMMUNICATION 2 |

| A. INTRODUCTION                                                   |

| B. HARDWARE                                                       |

| C. FIRMWARE                                                       |

| D. SOFTWARE9                                                      |

| E. SET-UP9                                                        |

| F. CONCLUSION10                                                   |

| PART 2: REAL-TIME PLAYBACK HARDWARE-IN-THE-LOOP SIMULATION OF     |

| TRAFFIC SYSTEMS 15                                                |

| A. INTRODUCTION15                                                 |

| B. LIMITATIONS IN MICROSCOPIC SIMULATIONS16                       |

| B. CONCLUSION                                                     |

| C. REFERENCES                                                     |

### **EXECUTIVE SUMMARY**

The controller interface device (CID) is the result of several years of hardware and software development by NIATT. This project had two objectives: the first was to expand the capability of the CID for applications where the number of input/output connections limit performance. The second objective was to investigate a new application area for CID technology, developing and testing a prototype to use the CID and CORSIM simulation to test traffic controller compliance to NTCIP communication standards.

This final report is made in two parts. The first describes the development of a synchronous data link control (SDLC) interface capability for the CID. The second part discusses the completion of the real-time playback system to test CID timing performance introduced in and is presented in the form of a paper titled: "Real-Time Playback Hardware-in-the-Loop Simulation of Traffic Systems," presented at IECON 2005, 32<sup>nd</sup> Annual Conference of the IEEE Industrial Electronics Society. This paper discusses the development of a software-controlled embedded system to evaluate the effect of communication latencies in hardware-in-the-loop simulation of traffic systems. The tool uses the Controller Interface Device (CID) hardware developed for hardware-in-the-loop simulation with modifications made to the firmware to support real-time playback (RTPB). RTPB simulators have been used in power systems as a cheap alternative to real-time simulators. In some cases RTPB is the only possible simulation method. This paper presents the application of RTPB to traffic simulations using actual traffic controller hardware.

### PART 1: SYNCHRONOUS DATA LINK CONTROL INTERFACE FOR INTERFACE FOR CONTROLLER INTERFACE DEVICE TO TRAFFIC CONTROLLER COMMUNICATION

### A. INTRODUCTION

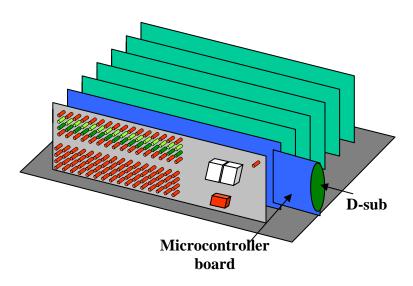

The synchronous data link control (SDLC) controller interface device (CID) is an adaptation of the original CID. The SDLC version replaces the original microcontroller board with a modified board that incorporates the original board in addition to a connector that allows for SDLC communication to TS/2 standard traffic controllers (see Fig. 1a and 1b). Neither the motherboard nor the daughterboards need to be modified. The CID case will need an additional cut out for the series port.

The benefit in using the new connector is that the SDLC link replaces over 80 wires with a single nine-wire RJ-45 cable by using high speed serial communications. Also, the SDLC link has additional features and modes that are not available in standard ABC type connectors for TS1 Controllers.

Figure 1a: SDLC microcontroller daughterboard compared to input, output and display boards.

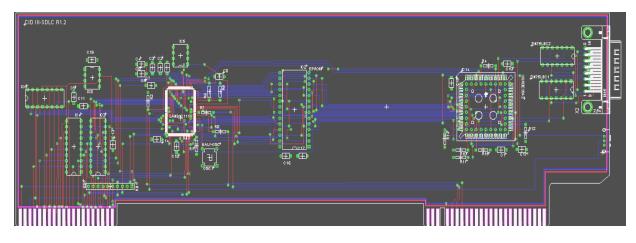

Figure 1b. SDLC CID Circuit Board

### **B. HARDWARE**

### 1. Revisions

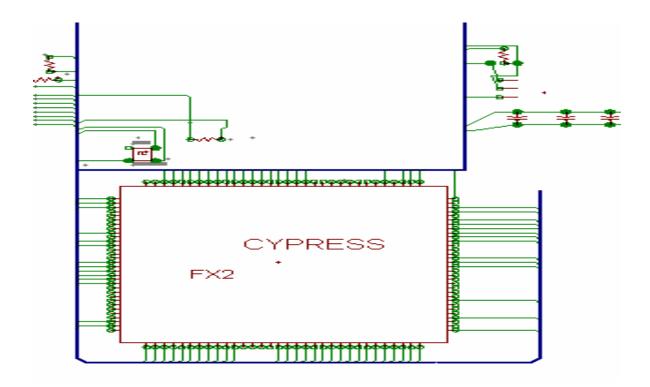

The main revisions include a change to a newer microcontroller; the Cypress FX2. The Cypress EZ- Universal Serial Bus (USB) AN2131 is now obsolete and the FX2 is an upgrade that allows use of the faster USB 2.0 protocol to communicate with the PC.

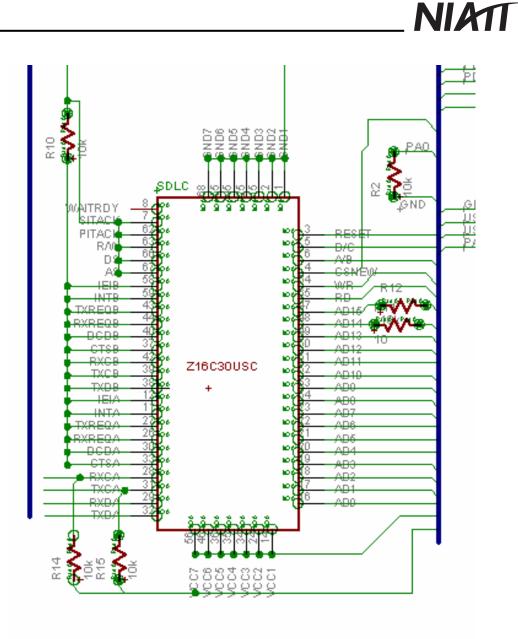

The second main revision is the inclusion of the Zilog Universal Serial Controller or USC (part number Z16C30) that is used for all SDLC communication processes such as error correction, parity checks, and conversions from parallel to the correct serial bit rate. The integrated circuit (IC) is highly adjustable however the firmware uses only the limited features needed to transfer over the SDLC port.

In order to switch between original and SDLC modes a two position switch is available on the right side of the microcontroller board. For SDLC mode the switch is the down position and for original the switch must be pressed in the upward position.

### 2. FX2 hardware interface

For proper utilization of the FX2 controller, an external 24 MHz parallel resonant crystal drives the on-chip electronics. For the USB connections, two resistances drop the output and input (USB+, USB-) line voltages. External supply to ground capacitances provide noise reduction to

the IC. External ports are driven from outputs and input pins. A 3.3 voltage regulator converts the 5V supply for proper supply voltage to the FX2 chip. A schematic diagram of this interface is shown in Figure 2.

Figure 2. FX2 Hardware Interface

### 3. SDLC Layout

The USC IC is interfaced to the FX2 through the available address and data buses. Read (RD), Write (WR) and Chip Select Strobes (CS) are carried directly from the FX2 output pins. Power and Ground lines are carried from the 5V power source. Pull-up resistors and Pull down resistors are used on any required floating pins as described in the USC manual.

Table 1 describes the pin connections required in the SDLC processor board. The interface to the USC is done strictly with command and data busses using built in data strobes for chip select, read and write functions. A schematic diagram of the SDLC circuit is shown in Fig. 3.

Figure 3. USC Layout

```

SDLC PINOUT LAYOUT

ZILOG USC

* * * * * * * * * * * *

D0 |----- AD0 - Data 0

D1 |----- AD1 - Data 1

D2 |----- AD2 - Data 2

D3 |----- AD3 - Data 3

D4 |-----| AD4 - Data 4

D5 |-----| AD5 - Data 5

D6 |----- AD6 - Data 6

D7 |----- AD7 - Data 7

A0 |----- | AD8 - U/L Selector 1 sets upper LSB

A1 |----- AD9 - USC Address0

A2 |-----| AD10 - USC Address1

A3 |-----| AD11 - USC Address2

A4 |-----| AD12 - USC Address3

A5 |-----| AD13 - USC Address5

A6 |-----| D/C -Sets Data or Control

A7 |-----| A/B -Sets Channel A - Default Channel A

RD |-----| RD -Read

WR |----- WR -Write

CS |-----| CS -Chip Select, Activated high for Bus Transfers

A15 |-----| CSnew -Chip Select, option2

* * * * * * * * * * * * * * *

```

### 4. Parts List

A complete list of the parts needed for the SDLC CID microcontroller board is shown in Table 2 along with estimated prices and suppliers.

| Part                             | Manufacturer        | Product Codes    |                   | Price    |

|----------------------------------|---------------------|------------------|-------------------|----------|

| Circuit Board                    | QTC Circuits        |                  |                   | \$ 50.00 |

| Cypress EZ-USB microcontroller   | Cypress             | AN2131QC         | 428-1307-ND       | \$ 10.53 |

| 12 MHz Clock                     | ECE Inc.            | OECS-2200B-120   | XC269-ND1         | \$ 2.64  |

| 3.3 V Voltage Regulator          | Linear Technology   | LT1121CN8-3.3    | LT1121CN8-3.3-ND1 | \$ 2.75  |

| 3 to 8 decoder                   | Philips Electronics | 74HCT238         |                   | \$ -     |

| Octal Transceiver                | Philips Electronics | 74HCT245         |                   | \$ -     |

| EPROM 8X 32k                     | ST Microelectronics | M27C256B-100D0   | С                 | \$ -     |

| Octal 3 state Transceiver        | Texas Instruments   | SN74HC245N       | 296-1584-5-ND     | \$ 0.53  |

| D-Type Transparent Latch         | Texas Instruments   | SN74HC245N       | 296-1596-5-ND     | \$ 0.53  |

| D Flip Flop with 3 state         | Texas Instruments   | SN74HC245N       | 296-1598-5-ND     | \$ 0.53  |

| USC                              | Zilog               |                  |                   | \$ -     |

| RS485 Transscievers              | Texas Instruments   | SN75LBC180AN     | 296-6881-5-ND     | \$ 2.36  |

| Conn PLCC Socket 68 Pos. thru He | ole                 | 940-99-068-24-00 | 0000ED80026-ND    | \$ 0.91  |

Table 2. SDLC CID Parts List

### C. FIRMWARE

The firmware for the SDLC CID is modified from the original CIDII firmware with changes to convert to the FX2 IC and additional code to interface with the USC transceiver.

The source code file USC.c contains necessary functions to write, read and initialize the USC chip in the desired mode described in the National Electric Manufacturers Association (NEMA) TS2 standard documentation. USC.h contains all USC bit descriptions and constants needed to set up and communicate with the serial controller.

Table 3. USC Mode Settings

| BYTE CMRMODE_L = $0x06$  |  |

|--------------------------|--|

| BYTE CMRMODE_H = $0x06$  |  |

| BYTE CCARMODE_L = $0x00$ |  |

| BYTE CCARMODE_H = $0x00$ |  |

| BYTE CCSRMODE_L = $0x00$ |  |

| BYTE CCSRMODE_H = $0x00$ |  |

| BYTE CMCR_L = $0x09$     |  |

| BYTE CMCR_H = $0x00$     |  |

| BYTE RMR_L = $0x02$      |  |

| BYTE RMR_H = $0x00$      |  |

| BYTE TMR_L = $0x02$      |  |

| BYTE TMR_H = $0x00$      |  |

| BYTE IOCR_L = $0x08$     |  |

| BYTE IOCR_H = $0x00;$    |  |

For a description of the microcontroller operation refer to the FX2 manual, which is available in the docs folder as well as online at the following URL: www.keil.com/dd/docs/datashts/cypress/fx2\_trm.pdf.

Table 4 lists the source code needed for the SDLC CID and descriptions of each of the files.

| Filename | Version | Description               |

|----------|---------|---------------------------|

| Fw.c     | 1.1     | Basic USB operation       |

| cid.c    | 1.1     | Basic CID operation       |

| cid.h    | 1.1     | CID constants             |

| Dscr.h   | 1.1     | USB Descriptor Table      |

| Misc.c   | 1.1     | Various CID functions     |

| Periph.c | 1.1     | Serial/USB Communications |

| Periph.h | 1.1     | Constants                 |

| USC.c    | 1.1     | USC functions             |

| USC.h    | 1.1     | USC constants/addresses   |

Table 4. Firmware Source Code

### D. SOFTWARE

The CID PC software applications will require several modifications. First, the USB communication mode between the PC and CID will need to changed. The original CID II software suite performed PC to CID communication using isochronous USB communication. However, this mode of does not have sufficient bandwidth for SLDDC operation. Instead, bulk mode transfers are required to perform real-time hardware in the loop simulation. Since the guaranteed timing of the isochronous mode operation is not available, it is important to ensure that there are no other data intensive devices using the USB interface on the PC other than CIDs.

A bulk read of the SDLC USC is done with a 0x00 write. A bulk write to the SDLC USC is done with a 0x01 write, followed by the bits desired to be written as described in the protocol shown in Table 5. The protocol used for transfers between the CID and SDLC is described in Tables 5 and 6.

Second, the CID software applications will require modification to account for the additional inputs and outputs available through the use SDLC communication. This will be most noticable with the suitcase tester application.

### E. SET-UP

### 1. Setting up the TS2 traffic controller is SDLC mode

Follow instructions in traffic controller users manual.

### 2. Setting up and connecting the SDLC CID

- Remove the original CID microcontroller board from the CID by gently pulling upwards on both edges of the board. Be sure to not touch any electronics while doing so.

- Into the empty slot, insert the SDLC CID microcontroller board. The parts on the board should be visible from the front of the CID and the SDLC CID serial board (15 pin Sub D connector) will be on the right edge of the CID.

- Ensure the CID has attached power cable by checking that the C connector to the traffic controller is connected.

• To check that the new board is connected properly switch on the rear power connection on the CID to on. The front L's on the CID should flash left to right. Now turn the power switch back to the off position. To put the CID into SDLC mode, switch the side SDLC switch on the new board to the down position.

### 3. Connecting to the PC and hardware testing

- Connect a USB cable to the rear of the CID to an available USB slot on the PC.

- Upon connection, the PC should make its standard enumeration sound and a message on the PC should pop up on the left side of the screen that shows the hardware is now available. If not follow instructions on installing SDLC CID drivers.

### 4. Run application software

Follow normal CID software operation procedure.

### F. CONCLUSION

A final version of the modifications to CID to allow SDLC communication between the CID and the traffic controller has been presented. The hardware, firmware and software design has been described.

Table 5. CID to PC Messages

| CID  | to PC n                                                       | nessage This is the       | message         | e that updates the | e PC with the TC        | Byte<br>#            | e Bit<br># | Function                | ] [ | Byte<br>#                 | Bit # | Function                  |

|------|---------------------------------------------------------------|---------------------------|-----------------|--------------------|-------------------------|----------------------|------------|-------------------------|-----|---------------------------|-------|---------------------------|

| outp | uts. To                                                       | initiate this transfer, t | mmand byte 0x01 | <i>π</i>           | <i>"</i> 0              | Load Switch 13 Red + | 1 F        | π                       | 0   | System Special Function 1 |       |                           |

|      | via BULK ENDPOINT OUT1 to the CID and then read BULK ENDPOINT |                           |                 |                    |                         |                      |            | Load Switch 13 Red -    | 1 1 |                           | 1     | System Special Function 2 |

|      |                                                               |                           |                 | and then read D    |                         |                      | 1          | Load Switch 13 Yellow + |     |                           | 2     | System Special Function 3 |

| IINI | for this                                                      | message.                  |                 |                    |                         |                      | 3          | Load Switch 13 Yellow - |     |                           | 3     | System Special Function 4 |

|      |                                                               |                           |                 |                    |                         | 10                   |            | Load Switch 13 Green +  |     | 16                        | 4     | 0                         |

|      |                                                               |                           |                 |                    |                         |                      | 5          | Load Switch 13 Green -  | 1 1 |                           | 5     | 0                         |

|      |                                                               |                           |                 |                    |                         |                      | 6          | Load Switch 14 Red +    |     |                           | 6     | 0                         |

| Byte |                                                               |                           | Byte            |                    |                         |                      |            |                         |     |                           |       | ·                         |

| #    | Bit #                                                         | Function                  | #               | Bit #              | Function                |                      | 7          | Load Switch 14 Red -    |     |                           | 7     | 0                         |

|      | 0                                                             | CID Number Bit 0          |                 | 0                  | Load Switch 6 Yellow +  |                      | 0          | Load Switch 14 Yellow + | 1 1 |                           | 0     | Status Bit A Ring 1       |

|      | 1                                                             | CID Number Bit 1          |                 | 1                  | Load Switch 6 Yellow -  |                      | 1          | Load Switch 14 Yellow - |     |                           | 1     | Status Bit B Ring 1       |

|      | 2                                                             | CID Number Bit 2          |                 | 2                  | Load Switch 6 Green +   |                      | 2          | Load Switch 14 Green +  |     |                           | 2     | Status Bit C Ring 1       |

|      | 3                                                             | CID Number Bit 3          | 1               | 3                  | Load Switch 6 Green -   |                      | 3          | Load Switch 14 Green -  |     |                           | 3     | Status Bit A Ring 2       |

| 0    | 4                                                             | CID Number Bit 4          | 5               | 4                  | Load Switch 7 Red +     | 11                   | 4          | Load Switch 15 Red +    | 1   | 17                        | 4     | Status Bit B Ring 2       |

|      | 5                                                             | CID Number Bit 5          |                 | 5                  | Load Switch 7 Red -     |                      | 5          | Load Switch 15 Red -    |     |                           | 5     | Status Bit C Ring 2       |

|      | 6                                                             | CID Number Bit 6          |                 | 6                  | Load Switch 7 Yellow +  |                      | 6          | Load Switch 15 Yellow + |     |                           | 6     | 0                         |

|      |                                                               |                           |                 |                    |                         |                      |            |                         |     |                           |       |                           |

|      | 7                                                             | CID Number Bit 7          |                 | 7                  | Load Switch 7 Yellow -  |                      | 7          | Load Switch 15 Yellow - |     |                           | 7     | 0                         |

|      | 0                                                             | Load Switch 1 Red +       |                 | 0                  | Load Switch 7 Green +   |                      | 0          | Load Switch 15 Green +  |     |                           | 0     | Phase 1 Phase On          |

|      | 1                                                             | Load Switch 1 Red -       |                 | 1                  | Load Switch 7 Green -   |                      | 1          | Load Switch 15 Green -  |     |                           | 1     | Phase 2 Phase On          |

|      | 2                                                             | Load Switch 1 Yellow +    |                 | 2                  | Load Switch 8 Red +     |                      | 2          | Load Switch 16 Red +    |     |                           | 2     | Phase 3 Phase On          |

| 1    | 3                                                             | Load Switch 1 Yellow -    | 6               | 3                  | Load Switch 8 Red -     | 12                   | 3          | Load Switch 16 Red -    |     | 18                        | 3     | Phase 4 Phase On          |

|      | 4                                                             | Load Switch 1 Green +     | Ū               | 4                  | Load Switch 8 Yellow +  | 12                   | 4          | Load Switch 16 Yellow + |     | 10                        | 4     | Phase 5 Phase On          |

|      | 5                                                             | Load Switch 1 Green -     |                 | 5                  | Load Switch 8 Yellow -  |                      | 5          | Load Switch 16 Yellow - |     |                           | 5     | Phase 6 Phase On          |

|      | 6                                                             | Load Switch 2 Red +       |                 | 6                  | Load Switch 8 Green +   |                      | 6          | Load Switch 16 Green +  |     |                           | 6     | Phase 7 Phase On          |

|      | 7                                                             | Load Switch 2 Red -       |                 | 7                  | Load Switch 8 Green -   |                      | 7          | Load Switch 16 Green -  |     |                           | 7     | Phase 8 Phase On          |

|      | 0                                                             | Load Switch 2 Yellow +    |                 | 0                  | Load Switch 9 Red +     |                      | 0          | TBC Auxiliary 1         | ] T |                           | 0     | Phase 1 Phase Next        |

|      | 1                                                             | Load Switch 2 Yellow -    | 1               | 1                  | Load Switch 9 Red -     |                      | 1          | TBC Auxiliary 2         |     |                           | 1     | Phase 2 Phase Next        |

|      | 2                                                             | Load Switch 2 Green +     |                 | 2                  | Load Switch 9 Yellow +  |                      | 2          | Preempt 1 Status        |     |                           | 2     | Phase 3 Phase Next        |

| 2    | 3                                                             | Load Switch 2 Green -     | 7               | 3                  | Load Switch 9 Yellow -  | 13                   | 3          | Preempt 2 Status        |     | 19                        | 3     | Phase 4 Phase Next        |

| 2    | 4                                                             | Load Switch 3 Red +       |                 | 4                  | Load Switch 9 Green +   | 13                   | 4          | 0                       |     | 19                        | 4     | Phase 5 Phase Next        |

|      | 5                                                             | Load Switch 3 Red -       | 1               | 5                  | Load Switch 9 Green -   |                      | 5          | 0                       |     |                           | 5     | Phase 6 Phase Next        |

|      | 6                                                             | Load Switch 3 Yellow +    |                 | 6                  | Load Switch 10 Red +    |                      | 6          | 0                       |     |                           | 6     | Phase 7 Phase Next        |

|      | 7                                                             | Load Switch 3 Yellow -    |                 | 7                  | Load Switch 10 Red -    |                      | 7          | 0                       |     |                           | 7     | 0                         |

| 3    | 0                                                             | Load Switch 3 Green +     | 8               | 0                  | Load Switch 10 Yellow + | 14                   | 0          | TBC Auxiliary 3         | ] [ | 20                        | 0     | Phase 8 Phase Next        |

|      | 1                                                             | Load Switch 3 Green -     | 1               | 1                  | Load Switch 10 Yellow - |                      | 1          | Free/Coord Status       |     |                           | 1     | Phase 1 Check             |

|      | 2                                                             | Load Switch 4 Red +       |                 | 2                  | Load Switch 10 Green +  |                      | 2          | Preempt 3 Status        |     |                           | 2     | Phase 2 Check             |

|      | 3                                                             | Load Switch 4 Red -       |                 | 3                  | Load Switch 10 Green -  |                      | 3          | Preempt 4 Status        |     |                           | 3     | Phase 3 Check             |

|      | 4                                                             | Load Switch 4 Yellow +    |                 | 4                  | Load Switch 11 Red +    |                      | 4          | Preempt 5 Status        | ] [ |                           | 4     | Phase 4 Check             |

| 1 | 5 | Load Switch 4 Yellow - |  |   | 5 | Load Switch 11 Red -    |    | 5 | Preempt 6 Status       |

|---|---|------------------------|--|---|---|-------------------------|----|---|------------------------|

|   | 6 | Load Switch 4 Green +  |  |   | 6 | Load Switch 11 Yellow + |    | 6 | 0                      |

|   | 7 | Load Switch 4 Green -  |  |   | 7 | Load Switch 11 Yellow - |    | 7 | 0                      |

|   | 0 | Load Switch 5 Red +    |  |   | 0 | Load Switch 11 Green +  |    | 0 | Timing Plan A          |

|   | 1 | Load Switch 5 Red -    |  |   | 1 | Load Switch 11 Green -  |    | 1 | Timing Plan B          |

|   | 2 | Load Switch 5 Yellow + |  |   | 2 | Load Switch 12 Red +    |    | 2 | Timing Plan C          |

| 4 | 3 | Load Switch 5 Yellow - |  | 9 | 3 | Load Switch 12 Red -    | 15 | 3 | Timing Plan D          |

| 4 | 4 | Load Switch 5 Green +  |  | 9 | 4 | Load Switch 12 Yellow + | 15 | 4 | Offset 1               |

|   | 5 | Load Switch 5 Green -  |  |   | 5 | Load Switch 12 Yellow - |    | 5 | Offset 2               |

|   | 6 | Load Switch 6 Red +    |  |   | 6 | Load Switch 12 Green +  |    | 6 | Offset 3               |

|   | 7 | Load Switch 6 Red -    |  |   | 7 | Load Switch 12 Green -  |    | 7 | Automatic Flash Status |

|    | 5 | Phase 5 Check |

|----|---|---------------|

|    | 6 | Phase 6 Check |

|    | 7 | Phase 7 Check |

|    | 0 | Phase 8 Check |

|    | 1 | 0             |

|    | 2 | 0             |

| 21 | 3 | 0             |

| 21 | 4 | 0             |

|    | 5 | 0             |

|    | 6 | 0             |

|    | 7 | 0             |

### Table 6. PC To CID Messages

| PC 1  | o CID    | Message This r                          | message    | is sen | t to the CID               | 1. | Byte | Bit # | Function                   | Byte # | Bit # | Function                 | Byte | # | Bit # | Function                   |

|-------|----------|-----------------------------------------|------------|--------|----------------------------|----|------|-------|----------------------------|--------|-------|--------------------------|------|---|-------|----------------------------|

| via a | a bulk t | ransfer on Endpoi                       | int 1. A   | comn   | nand byte of               |    |      | 0     | Test B                     |        | 0     | Pedestrian<br>Detector 5 |      |   | 0     | 0                          |

|       |          | t byte in this mess<br>an input update. |            |        |                            |    |      | 1     | Automatic Flash            |        | 1     | Pedestrian<br>Detector 6 |      |   | 1     | Address Bit 0              |

|       |          | is message.                             | 11115 1116 | Kes th | e total Size 23            |    |      | 2     | Dimming Enable             |        | 2     | Pedestrian<br>Detector 7 |      |   | 2     | Address Bit 1              |

|       |          | -                                       |            |        |                            |    | 10   | 3     | Manual Control<br>Enable   | 16     | 3     | Pedestrian<br>Detector 8 | 2    | 2 | 3     | Address Bit 2              |

|       |          |                                         |            |        |                            |    |      | 4     | Interval Advance           |        | 4     | 0                        |      |   | 4     | Address Bit 3              |

|       |          |                                         |            |        |                            |    |      | 5     | External Minimum<br>Recall |        | 5     | 0                        |      |   | 5     | Address Bit 4              |

|       |          |                                         |            |        |                            |    |      | 6     | External Start             |        | 6     | 0                        |      |   | 6     | 0                          |

| Byte  | Bit #    | Function                                | Byte       | Bit #  | Function                   |    |      | 7     | TBC On Line                |        | 7     | 0                        |      |   | 7     | 0                          |

| 0     | 0        | 0                                       | 5          | 0      | Detector 33<br>Call Status |    | 11   | 0     | Stop Time Ring 1           | 17     | 0     | 0                        | 23   | 3 | 0     | Phase 1 Pedestrian<br>Omit |

|       | 1        | 0                                       | 11         | 1      | Detector 34<br>Call Status |    |      | 1     | Stop Time Ring 2           |        | 1     | 0                        |      |   | 1     | Phase 2 Pedestrian<br>Omit |

|       | 2        | 0                                       |            | 2      | Detector 35<br>Call Status |    |      | 2     | Max II Selection<br>Ring 1 |        | 2     | 0                        |      |   | 2     | Phase 3 Pedestrian<br>Omit |

|       | 3        | 0                                       |            | 3      | Detector 36<br>Call Status |    |      | 3     | Max II Selection<br>Ring 2 |        | 3     | 0                        |      |   | 3     | Phase 4 Pedestrian<br>Omit |

|       | 4        | 0                                       | ]          | 4      | Detector 37<br>Call Status |    |      | 4     | Force Off Ring 1           |        | 4     | 0                        |      |   | 4     | Phase 5 Pedestrian<br>Omit |

|       | 5        | 0                                       | ]          | 5      | Detector 38<br>Call Status |    |      | 5     | Force Off Ring 2           |        | 5     | 0                        |      |   | 5     | Phase 6 Pedestrian<br>Omit |

|       | 6        | 0                                       | ] [        | 6      | Detector 39<br>Call Status |    |      | 6     | Call to NA 1               |        | 6     | Red Rest<br>Ring 1       |      |   | 6     | Phase 7 Pedestrian<br>Omit |

| -        | -        | 1                |   |   |

|----------|----------|------------------|---|---|

|          | 7        | 0                |   | 7 |

|          |          | Detector 1 Call  |   |   |

|          | 0        | Status           |   | 0 |

|          |          | Detector 2 Call  |   |   |

|          | 1        | Status           |   | 1 |

|          | <u> </u> | Olalas           |   |   |

|          |          | Detector 3 Call  |   |   |

|          | 2        | Status           |   | 2 |

|          | 2        | Sialus           |   | 2 |

|          |          | Detector 4 Call  |   |   |

| 1        | 3        | Status           | 6 | 3 |

|          | 3        |                  |   | 3 |

|          |          | Detector 5 Call  |   |   |

|          | 4        | Status           |   | 4 |

|          | _        | Detector 6 Call  |   | _ |

|          | 5        | Status           |   | 5 |

|          |          | Detector 7 Call  |   |   |

|          | 6        | Status           |   | 6 |

|          |          | Detector 8 Call  |   |   |

|          | 7        | Status           |   | 7 |

|          |          | Detector 9 Call  |   |   |

|          | 0        | Status           |   | 0 |

|          |          | Detector 10 Call |   |   |

|          | 1        | Status           |   | 1 |

|          |          | Detector 11 Call |   |   |

|          | 2        | Status           |   | 2 |

|          |          | Detector 12 Call |   |   |

| 2        | 3        | Status           | 7 | 3 |

| 2        |          | Detector 13 Call | ' |   |

|          | 4        | Status           |   | 4 |

|          |          | Detector 14 Call |   |   |

|          | 5        | Status           |   | 5 |

|          |          | Detector 15 Call |   | ~ |

|          | 6        | Status           |   | 6 |

|          |          | Detector 16 Call |   | U |

|          | 7        | Status           |   | 7 |

| <u> </u> | '        | Detector 17 Call |   | 1 |

| 3        | 0        | Status           | 8 | 0 |

|          |          |                  |   | 0 |

|          | 1        | Detector 18 Call |   | 4 |

|          | 1        | Status           |   | 1 |

|          | _        | Detector 19 Call |   | ~ |

|          | 2        | Status           |   | 2 |

|          |          | Detector 20 Call |   | - |

|          | 3        | Status           |   | 3 |

|          |          | Detector 21 Call |   |   |

|          | 4        | Status           |   | 4 |

|          |          |                  |   |   |

| Detector 40Walk Rest7Call Status7Modifier0Call Status0Detector 11Call Status0Detector 11Call Status1Detector 22Call Status1Detector 22Call Status1Detector 32Call Status12Pedestrian3Detector 442Detector 34Call Status12Pedestrian5Call Status500Detector 45404Call Status600Detector 48707Call Status700Detector 50101Call Status700Detector 53302Call Status1300Detector 531404Call Status1300Detector 56731Call Status600Call Status1401Call Status1401Call Status1401Detector 58151Call Status1401Call Status151Detector 61261Call Status151Detector 61322Call Status3Call to NA II <t< th=""><th></th><th></th><th>_</th><th>_</th><th></th><th></th></t<>                                                                                                                                                                   |          |             | _ | _  |   |               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------|---|----|---|---------------|

| Detector 41<br>Call StatusPedestrian<br>Detector 11Call Status1Detector 12Call Status1Detector 22Call Status2Detector 23Call Status12Pedestrian<br>Detector 34Call Status2Detector 35Call Status12Pedestrian<br>Detector 30Detector 44<br>Call Status3Detector 44Call Status500Detector 46<br>Call Status600Call Status700Detector 48<br>Call Status700Detector 51<br>Call Status100Detector 51<br>Call Status100Detector 52<br>Call Status1300Detector 54<br>Call Status1300Detector 55<br>Call Status1300Detector 56<br>Call Status1400Detector 57<br>Call Status1400Detector 57<br>Call Status1400Detector 57<br>Call Status1400Detector 59<br>Call Status1401Detector 60<br>Call Status1400Detector 60<br>Call Status1400Detector 60<br>Call Status1400Detector 60<br>Call Status1400Detector 60<br>Call Status1400Detector 60 |          | Detector 40 |   |    |   | Walk Rest     |

| 0Call Status0Detector 11Call Status1Pedestrian2Call Status1Detector 23Call Status1Detector 30Detector 442Detector 33Call Status1Pedestrian0Detector 45404Call Status400Detector 46505Call Status400Detector 47606Call Status700Detector 50701Call Status700Call Status700Detector 51202Call Status100Detector 52303Call Status400Detector 54501Call Status400Detector 55606Call Status400Detector 57601Call Status500Detector 57601Call Status730Detector 57730Detector 57730Detector 58791Call Status790Detector 59261Call Status150Detector 59 <t< td=""><td>7</td><td>Call Status</td><td></td><td></td><td>7</td><td>Modifier</td></t<>                                                                                                                                                                                        | 7        | Call Status |   |    | 7 | Modifier      |

| Detector 42<br>1Pedestrian<br>Detector 21Call StatusPedestrian<br>22Call StatusPedestrian<br>23Call StatusPedestrian<br>24Call StatusPedestrian<br>30Detector 45<br>4Pedestrian<br>34Call StatusPedestrian<br>30Detector 45<br>446Call Status0Detector 47<br>66Call Status0Detector 48<br>77Call Status0Detector 50<br>11Call Status0Detector 51<br>22Call Status0Detector 52<br>33Call Status0Detector 54<br>55Call Status0Detector 55<br>66Call Status0Detector 55<br>66Call Status0Detector 57<br>70Call Status0Detector 57<br>70Call Status0Detector 57<br>70Call Status0Detector 58<br>1<br>Call Status1Detector 58<br>71Call Status0Detector 60<br>314Detector 60<br>315Call Status16Detector 60<br>317Detector 61                                                                                                           |          | Detector 41 |   |    |   | Pedestrian    |

| 1Call Status1Detector 22Call Status $2$ Pedestrian<br>Detector 45<br>4 $2$ Pedestrian<br>Detector 33Call Status $2$ Pedestrian<br>Detector 45 $4$ $0$ 4Call Status $4$ $0$ $6$ $6$ 5Call Status $4$ $0$ $6$ $6$ 0Detector 46<br>Call Status $6$ $0$ $6$ 0Detector 48<br>Call Status $7$ $0$ $6$ 0Detector 50<br>1Call Status $7$ $0$ 0Call Status $7$ $0$ $6$ 0Detector 51<br>2 $2$ $0$ $7$ 0Detector 52<br>3 $3$ $0$ $7$ 0Detector 53<br>4 $4$ $0$ $7$ 0Detector 54<br>5 $5$ $0$ $7$ 0Detector 56<br>6Call Status $4$ $0$ 0Detector 56<br>6Call Status $4$ $0$ 0Detector 56<br>7 $6$ $0$ $7$ 0Call Status $7$ $7$ $3$ 0Detector 56<br>7 $7$ $7$ $3$ 0Detector 58<br>1 $14$ $7$ $9$ 0Call Status $7$ $3$ $7$ 0Call Status $7$ $3$ $7$ 0Call Status $7$ $7$ $7$ 0Call Status $7$ $7$ $7$ 0Call Status $7$ $7$ $7$ <                 | 0        | Call Status |   |    | 0 | Detector 1    |

| Detector 43<br>Call StatusPedestrian<br>Detector 3Detector 44<br>Call Status12Pedestrian<br>Detector 4Detector 45<br>4Call Status40Detector 46<br>5Call Status40Detector 46<br>5Call Status50Detector 47<br>6Call Status60Detector 48<br>770Detector 49<br>0Call Status70Detector 50<br>1Call Status10Detector 51<br>2Call Status20Detector 53<br>4Call Status20Detector 54<br>5Call Status10Detector 55<br>6Call Status40Detector 55<br>6Call Status40Detector 56<br>7Call Status60Detector 57<br>0Call Status14Preempt DetectorDetector 58<br>1Call Status14Preempt DetectorDetector 59<br>2Call Status140Detector 59<br>2Call Status140Detector 58<br>1Call Status140Detector 60<br>3Call Status3Call to NA IIDetector 60<br>3Call Status3Call to NA II                                                                         |          | Detector 42 |   |    |   | Pedestrian    |

| 2Call Status12Detector 30Detector 443Detector 454Call Status400Detector 46505Call Status500Detector 47606Call Status700Detector 48707Call Status700Call Status700Call Status700Call Status700Call Status700Detector 50101Call Status200Detector 51202Call Status1300Detector 55606Call Status500Detector 55601Call Status500Call Status500Call Status500Call Status601Call Status1401Call Status150Call Status151Call Status151Call Status151Call Status152Call Status151Call Status151Call Status261Call Status3Call to NA II <td>1</td> <td>Call Status</td> <td></td> <td></td> <td>1</td> <td>Detector 2</td>                                                                                                                                                                                                                  | 1        | Call Status |   |    | 1 | Detector 2    |

| 2Call Status12Detector 30Detector 443Detector 454Call Status400Detector 46505Call Status500Detector 47606Call Status700Detector 48707Call Status700Call Status700Call Status700Call Status700Call Status700Detector 50101Call Status200Detector 51202Call Status1300Detector 55606Call Status500Detector 55601Call Status500Call Status500Call Status500Call Status601Call Status1401Call Status150Call Status151Call Status151Call Status151Call Status152Call Status151Call Status151Call Status261Call Status3Call to NA II <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                         |          |             |   |    |   |               |

| Detector 44<br>Call Status12Pedestrian<br>Detector 4123Detector 4123Detector 4123Detector 4123Detector 412123121231212121212121212121212121212121212121312121412121512131514141614141714141814151115141214141314141415141515141416141714181419141014110111111121113111311131113111311131113111311131113111311131113111311131113111311131113111311131113111311131113111311131113111311131113 </td <td></td> <td>Detector 43</td> <td></td> <td></td> <td></td> <td>Pedestrian</td>                                                                                                                                                                                                                                                                                                                                                  |          | Detector 43 |   |    |   | Pedestrian    |

| 3Call Status123Detector 40Detector 4540404Call Status50505Call Status50600Detector 4870007Call Status7000Call Status7000Call Status7000Call Status1000Detector 501101Call Status1000Detector 512012Call Status13300Detector 523303Call Status4010Detector 556016Call Status5010Call Status6010Call Status14040Detector 576040Call Status14040Detector 581501Call Status1510Detector 592612Call Status3Call to NA II0Detector 603Call Status0Detector 6115                                                                                                                                                                                                                                                                                                                                                                          | 2        | Call Status |   |    | 2 | Detector 3    |

| 3Call Status123Detector 40Detector 4540404Call Status50505Call Status50600Detector 4870007Call Status7000Call Status7000Call Status7000Call Status1000Detector 501101Call Status1000Detector 512012Call Status13300Detector 523303Call Status4010Detector 556016Call Status5010Call Status6010Call Status14040Detector 576040Call Status14040Detector 581501Call Status1510Detector 592612Call Status3Call to NA II0Detector 603Call Status0Detector 6115                                                                                                                                                                                                                                                                                                                                                                          |          |             |   |    |   |               |

| 3Call Status3Detector 40Detector 45404Call Status500Detector 47606Call Status700Detector 48707Call Status700Call Status700Call Status700Call Status700Detector 50101Call Status100Detector 51202Call Status100Detector 53404Call Status400Detector 54505Call Status600Detector 56730Detector 57040Call Status730Detector 58151Call Status14Preempt Detector1Call Status150Call Status150Detector 59262Call Status3Call to NA II0Detector 603Call Status0Detector 613Call to NA II                                                                                                                                                                                                                                                                                                                                                  |          | Detector 44 |   | 10 |   | Pedestrian    |

| 4Call Status40Detector 465Call Status50Detector 476060Detector 487Call Status70Detector 490Call Status70Detector 501Call Status70Detector 512Call Status10Detector 523Call Status10Detector 523Call Status30Detector 534Call Status40Detector 545013Detector 556Call Status50Detector 5673140Detector 581501Detector 581419Preempt Detector1Call Status1415Detector 570415Detector 581501Detector 592Call Status141Detector 592615Detector 603Call Status3Call to NA IIDetector 61153Call to NA II                                                                                                                                                                                                                                                                                                                                 | 3        | Call Status |   | 12 | 3 | Detector 4    |

| Detector 465Call StatusDetector 476Call Status7Call Status7Call Status7Call Status7Call Status7Call Status7Call Status9Call Status9Call Status9Detector 501Call Status9Detector 512Call Status9Detector 523Call Status9Detector 534Call Status9Detector 545Call Status9Detector 556Call Status9Detector 570Call Status9Detector 581Call Status1Call Status1Detector 581Call Status1Detector 592Call Status1Detector 603Call Status1Detector 603Call Status1Detector 61                                                                                                                                                                                                                                                                                                                                                             |          | Detector 45 |   |    |   |               |

| 5Call Status50Detector 47600Detector 48707Call Status700Call Status700Call Status700Call Status100Detector 50111Call Status100Detector 51202Call Status200Detector 52333Call Status400Detector 54505Call Status400Detector 55606Call Status600Call Status730Detector 57040Call Status14Preempt Detector1Call Status150Detector 58151Call Status150Detector 59262Call Status3Call to NA II0Detector 603Call Status0Detector 6115                                                                                                                                                                                                                                                                                                                                                                                                    | 4        | Call Status |   |    | 4 | 0             |

| 5Call Status50Detector 47600Detector 48707Call Status700Call Status700Call Status700Call Status100Detector 50111Call Status100Detector 51202Call Status200Detector 52333Call Status400Detector 54505Call Status400Detector 55606Call Status600Call Status730Detector 57040Call Status14Preempt Detector1Call Status150Detector 58151Call Status150Detector 59262Call Status3Call to NA II0Detector 603Call Status0Detector 6115                                                                                                                                                                                                                                                                                                                                                                                                    |          | Detector 46 |   |    |   |               |

| Detector 476Call Status0Detector 48707Call Status700Call Status700Call Status700Call Status100Detector 50111Call Status200Detector 51202Call Status200Detector 52333Call Status400Detector 53404Call Status400Detector 54505Call Status600Detector 56730Detector 57040Call Status14Preempt Detector1Call Status150Detector 58151Call Status150Detector 59262Call Status3Call to NA II0Detector 603Call Status0Call Status3Call to NA II                                                                                                                                                                                                                                                                                                                                                                                            | 5        |             |   |    | 5 | 0             |

| 6Call Status60Detector 48707Call Status70Call Status70Call Status10Detector 5011Call Status10Detector 5122Call Status20Detector 5233Call Status10Detector 523Call Status40Detector 545Call Status0Detector 556Call Status0Detector 567Call Status0Detector 570Call Status0Detector 581Call Status0Detector 581Call Status0Detector 592Call Status0Detector 592Call Status0Detector 603Call Status0Call Status0A1Detector 603Call Status0Call Status0A1Detector 603Call Status0Call Status0A1Detector 61                                                                                                                                                                                                                                                                                                                            |          |             |   |    |   |               |

| Detector 4870Call Status70Detector 4900Detector 5011Call Status10Detector 5120Call Status20Detector 523Call StatusDetector 534Call StatusDetector 5430Detector 556Call StatusDetector 56607Call Status6Detector 5673Detector 58149Detector 5915Detector 5915Detector 5915Detector 603Call StatusDetector 619Detector 619                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6        |             |   |    | 6 | 0             |

| 7Call Status70Detector 490Call Status00Detector 501Call Status10Detector 512Call Status102Call Status2012Call Status1003Call Status1014Call Status13305Call Status4010Detector 534404Call Status4015Call Status600Detector 56737Call Status730Detector 5814Preempt Detector1Call Status1490Detector 59262Call Status150Detector 60323Call Status3Call to NA II                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -        |             |   |    | - | -             |

| Detector 49<br>0OO1Call Status101Call Status102Call Status102Call Status203Call Status203Call Status1334Call Status405Call Status400Detector 54505Call Status600Detector 55606Call Status730Detector 57040Call Status730Detector 5814Preempt Detector1Call Status1490Detector 59262Call Status260Detector 603Call Status0Detector 613Call to NA II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7        |             |   |    | 7 | 0             |

| 0Call Status001Call Status101Call Status102Call Status203Call Status204Call Status205Call Status400Detector 53404Call Status400Detector 54505Call Status600Detector 56767Call Status730Detector 5814Preempt Detector1Call Status1490Detector 59262Call Status150Detector 59262Call Status150Detector 603Call Status0Detector 603Call Status0Detector 613Call to NA II                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |             |   |    |   | •             |

| Detector 501Call Status2Call Status2Call Status3Call Status4Call Status5Call Status4Call Status5Call Status6Call Status5Call Status6Call Status6Call Status6Call Status6Call Status6Call Status6Call Status7Call Status6O7Call Status6O7Call Status1Call Status<                                                                                                                                                                                           | 0        |             |   |    | 0 | 0             |

| 1Call Status102Call Status203Call Status13203Call Status13304Call Status4045Call Status405Call Status506Call Status600Detector 55606Call Status600Detector 57600Call Status14Preempt Detector1Call Status1490Detector 59262Call Status1450Detector 60323Call Status3Call to NA II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | •        |             |   |    | Ū | <u> </u>      |

| Detector 51<br>Call Status202Call Status13203Call Status13304Call Status4045Call Status405Call Status500Detector 55606Call Status600Detector 56730Detector 57600Call Status14Preempt Detector1Call Status1490Detector 59262Call Status1450Detector 59262Call Status150Detector 603Call Status0Detector 613Call to NA II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1        |             |   |    | 1 | 0             |

| 2Call Status203Call Status13304Call Status4304Call Status4405Call Status4045Call Status500Detector 55606Call Status600Detector 56730Detector 57730Call Status14Preempt Detector1Call Status1490Detector 59262Call Status150Detector 603Call Status0Detector 613Call to NA II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <u> </u> |             |   |    | • | •             |

| Detector 523Call Status13133013133013240132401401015135016010171350181313131914141411141414111414141114141412141414131414141414141415141514161415141715141518141514191415141115141511151415121415141314151414151515151515161616161617161616181616161916161619161616191616161916161619161616191616161916161619161616 <tr< td=""><td>2</td><td></td><td></td><td></td><td>2</td><td>0</td></tr<>                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2        |             |   |    | 2 | 0             |

| 3Call Status13304Call Status40405Call Status40565Call Status50566Call Status60600Detector 5673607Call Status73730Detector 57731490Call Status14040Call Status14991Call Status14592Call Status1592Call Status1592Call Status3Call to NA II0Detector 603Call to NA II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2        |             |   |    | - | •             |

| Detector 53<br>Call Status134Call Status5Call Status5Call Status6Call Status0Detector 556Call Status0Detector 567Call Status0Call Status0Call Status0Detector 570Call Status1Call Status0Detector 581Call Status0Detector 592Call Status0Detector 603Call Status0Call Status1Detector 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3        |             |   |    | З | 0             |

| 4Call Status40Detector 545Call Status50Detector 556Call Status60Detector 567Call Status607Call Status73Detector 577314Preempt Detector0Call Status1404Detector 581501Call Status149Detector 592Call Status1Detector 603Call Status3Detector 613Call to NA II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0        |             |   | 13 |   | •             |

| Detector 545Call StatusDetector 556Call Status0Detector 567Call Status0Detector 570Call Status1Call Status0Detector 581Call Status1Call Status1Detector 592Call Status0Detector 603Call Status0Call Status1Call Status1S0Detector 603Call Status0Call Status1S0Call Status1S1Call Status1S1Call Status1S1Call Status1S1S1S1S1S1S1S1S1S1S1S1S1S1S1S1S1S1S1S1S1S1S1S1S1S1S1S1S1S1S1S1S2<                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4        |             |   |    | 1 | 0             |

| 5Call Status500Detector 55606Call Status600Detector 56730Call Status730Call Status1400Call Status1490Detector 58151Call Status150Detector 59262Call Status260Detector 603Call Status0Detector 613Call to NA II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -        |             |   |    | - | 0             |

| Detector 556Call Status60Detector 567Call Status73Detector 577314Preempt Detector0Call Status1404Detector 5815Preempt Detector1Call Status15Detector 592Call Status22Call Status263Call Status3Call to NA II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Б        |             |   |    | Б | 0             |

| 6Call Status60Detector 567Call Status73Detector 570Call Status14Preempt Detector0Call Status1404Detector 5815Preempt Detector1Call Status15Detector 592Call Status22Call Status26Detector 603Call Status3Detector 6143Call to NA II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5        |             |   |    | 5 | 0             |

| Detector 56Preempt Detector7Call Status73Detector 570Call Status14Preempt Detector0Call Status1404Detector 5815Preempt Detector1Call Status15Detector 592Call Status22Call Status3Call to NA IIDetector 603Call to NA II11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6        |             |   |    | 6 | 0             |

| 7Call Status730Detector 57014Preempt Detector0Call Status14040Detector 58151Call Status152Call Status263Call Status3Call to NA IIDetector 61111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0        |             |   |    | 0 |               |

| Detector 57<br>0Detector 57<br>Call Status14Preempt Detector<br>4Detector 58<br>1Call StatusPreempt Detector<br>11Detector 59<br>2Call StatusPreempt Detector<br>26Detector 60<br>3Call Status3Call to NA IIDetector 61Detector 6111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7        |             |   |    | 7 |               |

| 0Call Status1404Detector 58Preempt Detector1Call StatusDetector 59Preempt Detector2Call StatusDetector 603Call StatusDetector 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1        |             |   |    | 1 | -             |

| Detector 58Preempt Detector1Call Status15Detector 59Preempt Detector22Call Status26Detector 603Call Status3Detector 613Call to NA II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0        |             |   | 14 | ~ |               |